#### The "BAREFOOT" ENGINEER

#### Presented by John Brock

John Brock is an electronics engineer with over 20 years experience in the electronics industry, with the last 5 years concerned with microprocessor based development. He has designed communications equipment for the South African Air Force as well as time and attendance systems. He also has designed a series of microcontrollers for time and data process applications. In more recent times he has written communications and network applications software for the PC. As an independent consultant he provides development, support and backup facilities for individual and corporate clients.

As a support person you need tools to test and diagnose PC problems. The aim of this course is to provide you with your own tools. These tools you will generate, using the software provided with DOS. Such tools include the use of DEBUG and QBasic or BASIC. An understanding of the hardware and the way it is interconnected will also be provided to help you find the majority of faults. The emphasis will be on the practical aspects.

Most PC problems today stem from incorrect configuration of either the system hardware or the operating system. So I have added a sizeable section on configuration of the machine.

Software tools are available, but at a price and operate usually without the users understanding. You probably know half a dozen users who have a copy of PCTOOLS or NORTON and profess to use it regularly. One user of mine insisted that he had to have PCTOOLS on his hard disk. He got a copy somehow, and promptly formatted his hard disk!

I have found over the years that the best tools are the ones you make yourself, and the next best, the ones you know how they work. So with that in mind, I am going to show you how to build your own tools for testing the PC.

| THE "BAREFOOT" ENGINEER                                       | 1  |

|---------------------------------------------------------------|----|

| SECTION 1COMPUTER FUNDAMENTALS - BUILDING BLOCKS IN HARDWARE. |    |

| A brief history of the PC                                     |    |

| The components of the microcomputer                           | 8  |

| The Central Processing Unit (CPU)                             |    |

| The Memory                                                    |    |

| The Input Unit                                                |    |

| The Output Unit                                               |    |

| A simple microprocessor system                                |    |

| Intel's microprocessor family                                 |    |

| 8086 & 8088                                                   |    |

| Block diagram of 8088/86                                      |    |

| 8088/8086 Registers                                           |    |

| 80188 & 80186                                                 |    |

| 80286                                                         |    |

| 80386                                                         |    |

| How the processors improved                                   |    |

| 80486                                                         |    |

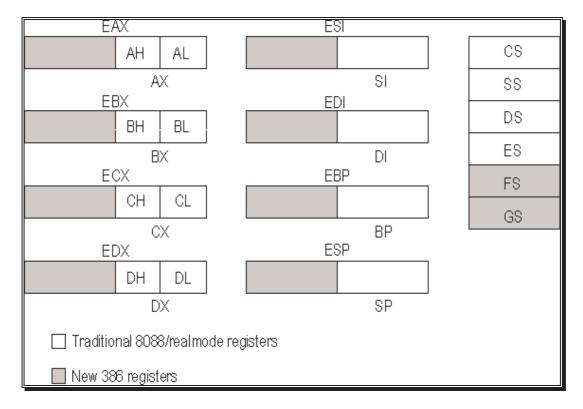

| The extensions to the 8086 registers in the 80386/80486       | 15 |

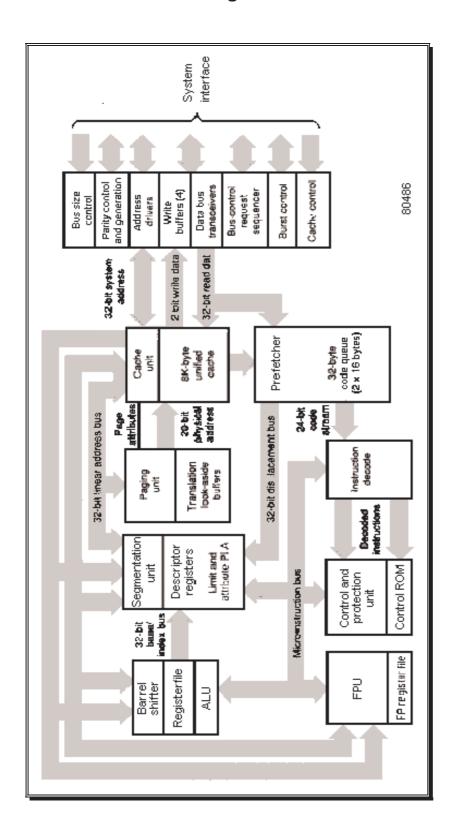

| The 80486DX Block diagram                                     | 16 |

| The "Pentium"                                                 | 17 |

| The P6 now "Pentium Pro"                                      | 17 |

| Klamath and MMX processors                                    | 18 |

| The Pentium II                                                | 19 |

| Multiprocessor computers                                      | 20 |

| 8087, 80287 and 80387 Floating point coprocessors             | 20 |

| 8087 Coprocessor block diagram                                | 20 |

| Support Microcontrollers                                      | 21 |

| DMA (Direct Memory Access) Microcontroller                    | 21 |

| Clock Generator and Timing Crystals                           | 21 |

| PIT (Programmable Interval Timer)                             |    |

| Programmable Peripheral Interface (PPI)                       | 22 |

| The Keyboard interface controller                             |    |

| Interrupt Controller                                          | 22 |

| The Floppy disk drive controller                              | 22 |

| The hard disk controller                                      | 22 |

| Wait state                                                    | 23 |

| Memory, memory addressing & structure                         | 24 |

| Memory                                                        | 24 |

| ROM (Read Only Memory)                                        |    |

| RAM (Random Access Memory)                                    |    |

| Parity - Hardware error detection                             | 25 |

| Mix-n-Match its not                                           | 26 |

| Memory Addressing                                             | 26 |

| Intel Notation                                                | 27 |

| Looking at Memory addresses with Debug                        | 27 |

| The PC's Memory Structure                                     |    |

| The XT & AT System memory map                                 |    |

| Port & I/O Addressing                                         |    |

| XT (8088) I/O Address map                                     |    |

| AT & ISA I/O Address Map                                      |    |

| Peripheral Devices                                            |    |

| Display adapters                                              |    |

| Color Graphics Adapter *                                      |    |

| The VGA adapter                                               |    |

| Local Bus VGA adapters                                        |    |

| PCI VGA cards                                                 |    |

|     | Accelerated Graphics Port - AGP                                   | 35 |

|-----|-------------------------------------------------------------------|----|

|     | Parallel and Serial communications                                | 36 |

|     | Voltage levels                                                    | 36 |

|     | Serial data communications and UARTS                              | 36 |

|     | Serial data stream                                                | 36 |

|     | The 8250 register set                                             |    |

|     | RS232C                                                            |    |

|     | Centronics Interface                                              |    |

|     | SCSI                                                              |    |

|     | A typical SCSI hard disk                                          |    |

|     | IDE - Integrated Drive Electronics                                |    |

|     | CD ROM drives                                                     |    |

|     | Tape Streamers                                                    |    |

|     | Helical scan recording                                            |    |

|     | Magneto-Optical Storage                                           |    |

|     | Scanners - Hand, Flat Bed                                         |    |

|     | Plotters, printers and other output devices                       |    |

|     | Mice, Digitisers and pads                                         |    |

|     | The System Bus Structure                                          |    |

|     | Control Bus                                                       |    |

|     | Address Bus                                                       |    |

|     | Data Bus                                                          |    |

|     | Bus Architectures - Expansion buses                               |    |

|     | Interrupts                                                        |    |

|     | When an interrupt occurs, the processor has to:                   |    |

|     | Software interrupt vectors & memory structure                     |    |

|     | System Configuration                                              |    |

|     | The XT dip switch                                                 |    |

|     | The Equipment Information Settings and Setup                      |    |

|     | Hard Disk table entries                                           |    |

|     | Low Level Formatting of Hard Disk                                 |    |

|     | The 528MB Barrier                                                 |    |

|     |                                                                   |    |

|     | CPU Speed Enhancement  Communicating with the outside world       |    |

|     | Terminal emulators                                                |    |

|     |                                                                   |    |

|     | Modems                                                            |    |

|     | Modem Standards                                                   |    |

|     | Some common standards:                                            |    |

|     | Talk to your Modem                                                | 57 |

|     | How to talk to a modem [politely]                                 |    |

|     | HAYES AT commands                                                 |    |

|     | Example command strings                                           |    |

|     | Extended HAYES AT commands                                        |    |

| 0.5 | Command descriptions                                              |    |

| 9E  | SCTION 2.0 SOFTWARE, FIRMWARE & OPERATING SYSTEM SOFTWARE         | 63 |

|     | BIOS - The Basic Input / Output System                            |    |

|     | Its a Windows World                                               |    |

|     | 'MS-DOS Compatible' and 'ROM BIOS Compatible'                     |    |

|     | A Bios function example                                           |    |

|     | BIOS Shadowing                                                    |    |

|     | The ROM BIOS Date                                                 |    |

|     | Programs that change the port addresses in the ROM BIOS Data area |    |

|     | DOS Startup                                                       |    |

|     | The "BOOT" Sector                                                 |    |

|     | The Boot sector structure                                         |    |

|     | The 32 Megabyte barrier                                           |    |

|     | The Partition table                                               |    |

|     | Partition structure                                               | 68 |

|    | The DOS System files                                                  | 68 |

|----|-----------------------------------------------------------------------|----|

|    | The Command Interpreter                                               | 69 |

|    | DOS' Disk structures                                                  |    |

|    | Clusters and allocation units                                         | 69 |

|    | The Directory entry                                                   | 70 |

|    | The File Allocation Table (FAT)                                       | 70 |

|    | Some FAT entries                                                      | 70 |

|    | MS-DOS Features                                                       | 71 |

|    | DOS Utility Programs                                                  | 72 |

|    | Mirror                                                                | 72 |

|    | Share                                                                 | 72 |

|    | Undelete - How to protect against accidental/deliberate file deletion | 72 |

|    | DOS Performance enhancers                                             | 73 |

|    | DOS' Limitations                                                      | 73 |

|    | Memory Configuration                                                  | 74 |

|    | The High memory area                                                  | 74 |

|    | Extended Memory Management (Himem.sys)                                | 74 |

|    | Upper Memory Blocks UMB's                                             |    |

|    | EMM386.EXE and Upper Memory                                           | 76 |

|    | Using MEM to check upper memory                                       | 77 |

|    | Example MEM output using the /c option:                               | 78 |

|    | Memory Configuration Fault Finding                                    | 79 |

|    | Other operating systems                                               | 80 |

|    | Windows 3.x and Windows for Workgroups                                | 80 |

|    | Windows 95/98                                                         |    |

|    | OS/2 2.1 - 3.0 "Warp Connect"                                         |    |

|    | Windows NT (Now NT4 Server & Workstation)                             |    |

|    | Multitasking Systems                                                  | 81 |

|    | What is multitasking?                                                 |    |

|    | Windows vs OS/2                                                       |    |

| _  | Windows NT vs OS/2                                                    |    |

| SE | CTION 3 PROBLEM AREAS                                                 | 82 |

|    | Hardware handling - STATIC                                            |    |

|    | Radio Frequency Interference (RFI)                                    |    |

|    | What happens when it goes wrong. Fault finding                        |    |

|    | Lightning                                                             |    |

|    | The Post Office "Five Point Scheme"                                   |    |

|    | Backup                                                                |    |

|    | PkZip options for making a full and incremental backup                |    |

|    | Windows troubleshooting                                               |    |

|    | General Protection Fault                                              |    |

|    | General Protection Fault (Interrupt 13)                               |    |

|    | Stack Fault (Interrupt 12)                                            |    |

|    | Invalid Instruction (Interrupt 6)                                     |    |

|    | Divide Error (Interrupt 0)                                            |    |

|    | Segment Load Failure                                                  |    |

|    | The Win /B option and others                                          |    |

|    | Section 4 Comedy in computing - keeping your sense of humour.         |    |

|    | Section 5 Information, we want information.                           |    |

|    | Looking after your information - support, diagnostics, tools          |    |

|    | Packetisation of data - X25                                           |    |

|    | Section 6 The Standard PC Specification                               |    |

|    | Processor of choice (best bang for the buck)                          |    |

|    | Cpu manufacturer AMD or Intel or Cyrix/TI                             |    |

|    | Memory                                                                |    |

|    | Hard Disk                                                             |    |

|    | Disk performance                                                      |    |

|    | POINT POLITICITION                                                    | ∪∠ |

| Video Display Adapter                                            | 93  |

|------------------------------------------------------------------|-----|

| Display Monitor                                                  |     |

| Serial ports (Com1 to 4)                                         |     |

| Parallel Ports (Lpt1 to 3)                                       |     |

| Sound Card (Microphone, line input, line output, speaker output) |     |

| Power Supply                                                     |     |

| Section 7 New developments in computing                          |     |

| New developments in PC technology                                |     |

| APPENDIX A : Other Number Systems                                |     |

| APPENDIX B : SCREEN MODES REFERENCE                              | 97  |

| MDPA, CGA, Hercules, Olivetti, EGA, VGA, or MCGA Adapters        | 97  |

| CGA, EGA, VGA, or MCGA Adapters                                  |     |

| Hercules, Olivetti, or AT&T Adapters                             |     |

| EGA or VGA Adapters                                              |     |

| EGA or VGA Adapters, Monochrome Monitor Only                     | 98  |

| VGA or MCGA Adapters                                             | 98  |

| APPENDIX C: EMM386.EXE REFERENCE                                 | 99  |

| APPENDIX D: THE 8250 REGISTER SET                                | 104 |

| APPENDIX E: PC AND XT BUS SIGNAL LINES                           | 106 |

| Additional Signal Lines for the 16-bit ISA bus                   | 107 |

| Signal lines added to ISA to create EISA                         |     |

| AT (80286) Hard disk table parameters                            |     |

| Appendix D: The 8250 register set                                |     |

| Appendix E: PC AND XT Bus signal lines                           |     |

| Additional Signal Lines for the 16-bit ISA bus                   |     |

| Signal lines added to ISA to create EISA                         |     |

| BIBLIOGRAPHY                                                     | 115 |

### Section 1 Computer fundamentals - building blocks in hardware.

# A brief history of the PC

- 1951 The SAGE project links radar sites in the US at 1300Baud.

- 1961 Leonard Kleinrock of MIT publishes first paper on packet switching.

- 1968 Messrs Noyce and Moore leave Fairchild to found Intelligent Electronics (INTEL).

- 1971 4004 developed by INTEL developed for a calculator company called Busicom.

This first microprocessor was introduced by Intel in 1971 and was a 4-bit machine called the 4004. This was the first of its kind; a 4-bit machine, oriented towards calculators but capable of very much wider application.

- 1972 8008 8 bit processor follows the 4004.

The latter was superseded by the 8080, a 'N.M.O.S.' processor with a  $2\mu S$  instruction cycle and 70 instructions. The power dissipation is only 600 mW and there is a full range of r.o.ms and r.a.ms, clock and interface receivers and drivers so that a complete system could easily be built.

- 1973 Bob Metcalfe invents the "Ether Network" based on CSMA/CD.

- 1974 Vinton Cerf & Bob Kahn produce the protocol suite TCP/IP.

- 1975 MITS introduced the Altair 8800 using the 8080 256 bytes of memory, toggle switches for programming and LED front panel.

Z80, 6502 and 6800 all developed. Z80 became available in Feb 76.

KIM-1 single board computer 1k bytes of memory, 2k bytes of rom

IBM announced a 50-Pound briefcase size computer called the 5100. It had 16k Bytes of memory, BASIC and a 16 line by 64 character display with a magnetic tape storage system.

Bill Gates and Paul Allen found Microsoft and write microcomputer BASIC on punched tape!

1976 Apple 1 based on the 6502 built by Steve Jobs and Steve Wozniak. The Apple 1 had no case or power supply or peripherals. They proposed personal computer designs to both Hewlett Packard and Atari, both were rejected!

Texas Instruments released the TMS9000 a 16 bit microprocessor.

Cromemco released the Z-1 a Z80 system with 8k bytes of ram and serial I/O.

RCA introduced the 1802 microprocessor the first CMOS microprocessor.

Shugart released the "minifloppy" disk drive to use 5.25" disks.

1977 The Apple II is released using the 6502 and 16k bytes of memory expandable to 64k, 16k bytes of ROM, a keyboard, cassette interface, eight slot motherboard, game paddles, and colour capable graphics/text display.

The TRS-80 was brought out by Tandy Radio Shack. It used a Z80 and had 4k bytes of ram, 4k bytes of rom (including BASIC), a keyboard, display and cassette interface.

Gary Kildall develops CP/M which becomes the standard operating system for 8080/Z80 based pc's.

Commodore Business Machines unveils the PET based on the 6502.

1978 Epson introduces the MX80 dot matrix printer.

MicroPro international is founded and releases a word processor package called WordMaster.

Apple and Radio Shack both announce 5.25" disk drives.

Texas introduces Speak and Spell.

1979 Visicalc shown off by Dan Bricklin and Bob Frankston

Hayes releases a 110/300 Baud Micromodem which autodials and autoanswers.

Intel announces the 8088 and 8086.

Wayne Ratcliff develops the Vulcan program, which will later become dBase II.

Xerox, DEC and Intel announce Ethernet.

3Com is founded by Bob Metcalfe.

1980 Clive Sinclair releases the ZX80 based on the Z80 with only 1k ram, 4k rom Basic which plugged into a standard TV.

Commodore Vic 20 released.

Apple III finally released.

Shugart starts selling the Winchester drive hard disk.

CP/M 86 by Digital Research released.

WordPerfect for Data General computers.

1981 Osborne 1 portable/Luggable.

The IBM PC released.

Clive Sinclair produces the ZX81 to replace the ZX80.

# The components of the microcomputer.

All microcomputers contain similar components. These are the Central Processing Unit or Microprocessor, read only memory, read-write memory and the Input and Output (I/O) units.

### The Central Processing Unit (CPU)

The CPU consists of three components the ALU (Arithmetic Logic Unit), The Control Unit and the Registers. The ALU performs all calculations, comparisons and logical operations, using the registers for data manipulation. The coordination of the microprocessor, and the microcomputer, is done by the Control Unit. The interpretation of the programming instruction code and the generation of the internal and external control signals are also handled by the Control Unit. The CPU requires instructions before it can do anything, and these are placed into Read Only Memory by the manufacturer of the motherboard. Memory is accessed by the CPU by means of an address, data and control bus connecting structure. Input and Output "ports" are accessed in a similar manner.

### The Memory

The memory that is used in microcomputer systems is split into two types, the read-write or Random Access Memory (RAM) and the Read Only Memory (ROM). The main function of the memory is to store instructions or programs and data for use by the microprocessor.

# **The Input Unit**

Input is the way data is put into memory. The Input unit is a device that interfaces the microcomputer system to the outside world. Input units generally used are the keyboard, a mouse, serial interface, joystick adapter, etc.

# **The Output Unit**

When the micro computer has completed its computations, it must have some method of displaying the results. This method is known as output and the output units handle the display of information. The common output units include the monitor and the printer.

Devices such as hard and floppy disk drives, and modems are known as input/output devices as they are used for both input and output.

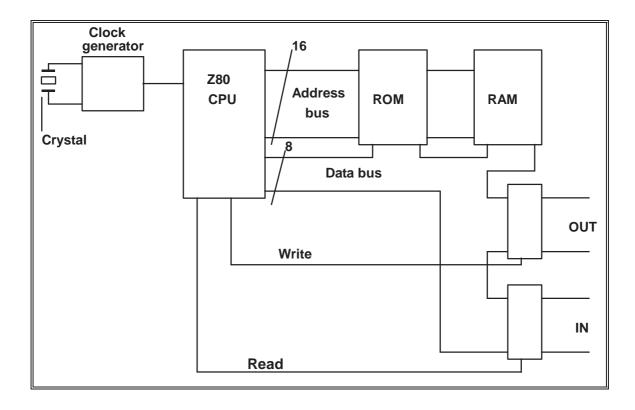

#### A simple microprocessor system

Our simple microprocessor starts operation by setting the address bus "bits" all to a logical zero. This corresponds to an address of zero. It then does a memory read of what is at the first location and this is placed onto the data bus by the ROM. It looks at the code it finds there up in an internal table, and proceeds to execute that instruction. The instruction may refer to the next location, if so it will set up the address bus accordingly to a logical one, and do another memory read. It will keep reading instructions from memory until it is either reset or it is told to wait for something to happen. One method of checking out the Z80 system was to tie the data bus to logical zero, and watch the address bus step from zero to 65535. This relied on the fact that the code for NOP, or no operation, was zero. Unfortunately that does not apply to the 8088 series of microprocessors.

The Z80 processor grew out of the development of the 8080 by INTEL. The operating system that became an industry standard based on both processors was the CP/M system. The diagram shown is a simplified version and does not show any "GLUE" chips. These chips would have been used to interconnect the major integrated circuits used in the complete system. These PC's preceded the advent of the IBM PC in 1981, and were still being sold and used in 1985.

# Intel's microprocessor family

The microprocessor used in the IBM compatible microcomputers is based on a CPU manufactured by INTEL or one of its competitors. Several microprocessors have been manufactured by Intel for the IBM PC range, these are the 8086 and 8088, the 80186 and 80188, 80286, 80386, 80386SX, 80486, 80486SX, the Pentium and Pentium Pro. The range of microprocessors also includes the 8087, the 80287, the 80387SX and the 80387. The x87 ranges of microprocessors assist the x86 range by handling floating point calculations. The coprocessors have been incorporated into the cpu from the 80486 up.

Plastic 8088 processor

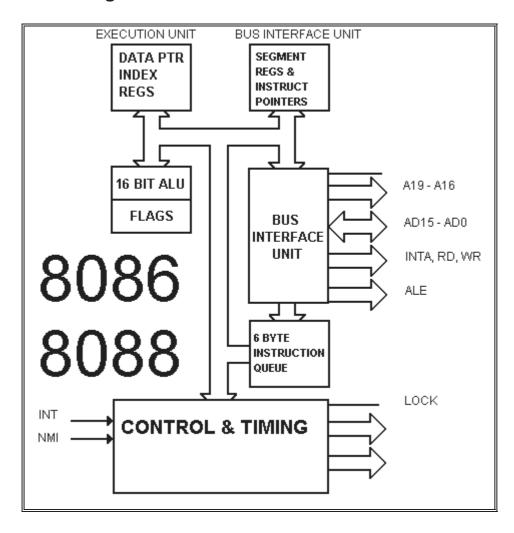

#### 8086 & 8088

The 8088 microprocessor was used to develop the original IBM PC. Other manufacturers of microprocessors have designed and marketed, other compatible microprocessors, under licence from Intel. These are NEC (V20 and V30), which amazingly could also be switched into a Z80 mode of operation.

The 8088 uses 16 bit sets for instruction and data manipulation, but will only output data in an 8 bit format. It is a 16 bit instruction, 8 bit data microprocessor. A 20 (A0 to A19) line address bus is used to access memory therefore the maximum amount of memory that it can access is 1024Kb or 1Mb. This is the reason PC DOS and MS DOS could only access 1Mb total memory without the aid of device drivers or Dos Extender software.

As the microprocessor runs it takes from a memory location an instruction, executes the instruction and then, unless the instruction directs otherwise, goes to the next memory location and repeats the process. If an instruction directs the microprocessor to access another area of memory, then the microprocessor will move the instruction retrieval to the new memory location and start processing from the specified point. Roughly 1 million instructions per second can be executed.

The differences between the 8088 and 8086 are that the 8086 will output data as 16 bit information. The 8088 is known, by Intel, as an 8 bit processor and the 8086 is a 16 bit processor. This is the only difference between the two processors. The 8086 is totally "code compatible" with the 8088. The 8086 was used in the IBM PS/2 model 25 and in some of the AT&T (Olivetti) microcomputers.

The original 8088 could run at a clock speed of 4.77MHz (Millions of Cycles per Second), however the 8088-2 and later versions ran at clock speeds up to 12MHz. These processors could be slowed down to 4.77MHz, by using a slower clock speed. This has been marketed as the 'Turbo' option. This is no longer a real option and turbo buttons should be disabled to stop users from accidentally slowing the pc.

The NEC V20 and V30 microprocessors were designed as plug in replacements for the 8088 and the 8086 and use much of the additional features of the 80188/6. Intel stopped production of the 8088 and 8086 microprocessors during 1988 and the Fujitsu and NEC have also stopped production of the 8088's manufactured under licence.

### Block diagram of 8088/86

One point to note about the diagram is that the address bus lines, AD0 to AD15 are shared with the 8 or 16 bit data bus. This was because the chips were made in 40 pin dual in line packages therefore not providing sufficient pins for connection. Later processors had more pins.

**NOTE:** The 6 byte instruction queue is a form of caching.

### 8088/8086 Registers

| AH<br>BH<br>CH<br>DX | -AX- AL<br>-BX- BL<br>-CX- CL<br>-DX- DL | ACCUMULATOR<br>BASE<br>COUNT<br>DATA                           |

|----------------------|------------------------------------------|----------------------------------------------------------------|

|                      | SP<br>BP<br>SI<br>DI                     | STACK POINTER BASE POINTER SOURCE INDEX DESTINATION INDEX      |

|                      | CS<br>DS<br>SS<br>ES                     | CODE SEGMENT<br>DATA SEGMENT<br>STACK SEGMENT<br>EXTRA SEGMENT |

|                      | IP                                       | INSTRUCTION POINTER                                            |

#### **FLAGS REGISTER**

| 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8  | 7  | 6  | 5 | 4  | 3 | 2  | 1 | 0  |

|----|----|----|----|----|----|----|----|----|----|---|----|---|----|---|----|

|    |    |    |    | OF | DF | IF | TF | SF | ZF |   | AF |   | PF |   | CF |

All the following processors including the Pentium II contain these registers with some additional registers and enhancements.

#### 80188 & 80186

Intel incorporated some extra features into this design and it was used in some XT type machines. It featured:-

an enhanced 8086-2 CPU clock generator 2 independent, high speed DMA channels a programmable interrupt controller 3 programmable 16 bit timers programmable memory and peripheral chip select logic programmable wait state generator local bus controller

It was available in versions with clock speeds of 8, 10 and 12 MHz. It still addressed only 1 megabyte of memory. It was however totally "code compatible" with the 8088/6. This processor is generally used for SCSI controllers and dedicated control functions.

#### 80286

This microprocessor was used as the CPU for the IBM PC/AT series of microcomputers. The 80286 for upward code compatibility contains the same instruction set as the 8086, but has increased and enhanced the total instruction set. This means that the 80286 can run the same operating systems and programs as the 8086/8. Several of the microcontroller support functions were also built into the 80286 these are:

Memory management circuitry that allowed the 80286 to use Protected mode and to access up to 16MB of memory.

Interrupt controller circuitry.

DMA control circuitry.

Bus cycle decoding circuitry.

These functions were previously handled by separate support microcontrollers on 8086 and 8088 motherboards. The result of this incorporation is that the 80286 has had the effect of allowing the 80286 motherboards to become smaller. Baby or XT sized AT motherboards are an example of this. Though the original AT motherboards were very large requiring special cases.

The 80286 has four internal units, which provided the enhanced functions. These are:

The Memory Manager allows the 80286 to access 16Mb of physical memory.

The Bus Controller controls a restrictive bus mastering concept.

The Instruction queue prefetch processor that speeds up the instruction usage.

The Execution unit was the same as the 8088 and 8086.

The external and internal bus widths of the 80286 are both 16 bits wide, this makes the microprocessor a true 16 bit processor. This was later referred to as the Industry Standard Architecture or ISA configuration. The Instruction processor enables the microprocessor to handle program code faster, as the next instruction from memory is fetched while the previous instruction is being executed.

With the Execution unit being similar to the CPU of the 8088 and 8086, the emulation of the earlier microprocessors was done at up to six times faster, when using the same clock speed. The clock speed was also variable and could range between 8MHz and 25MHz. The external clock frequency was twice the actual clock frequency used internally.

The protected mode of the 80286 was not used by DOS as this would have meant a complete rewrite of the operating system. Microsoft, in conjunction with IBM, based the original OS/2 operating system kernel on the protected mode. OS/2 was not available when the IBM PC/AT was released, so the standard operating system was PC DOS.

During this period software became able to use more and more memory. A typical program being Lotus 123. To aid the XT users a memory scheme called Expanded memory was devised. The three companies that developed the Expanded memory specification were Lotus Corporation, Intel and Microsoft. This became known as the "LIM" standard. This hardware was quite often added to AT motherboard designs.

#### 80386

With the release of this microprocessor the 32 bit standard that most new operating systems use was created. The 80386 has enjoyed a greater acceptance because the operating systems and programs would not have to be upgraded to be run at full capacity on later microprocessors.

The 80386 has the same functions as the 80286, but they have been improved and enhanced. The memory management unit can access 4 Gigabytes of memory directly and 16 Terabytes of virtual memory. Enhancements to the Bus controller allow full bus mastering to be controlled by the microprocessor. The real power of the 80386 lies in the Virtual mode of the microprocessor, enabling the microprocessor to emulate multiple 8086/8 microprocessors.

The speed range of the 80386 was also been improved to allow a speed of up to 33MHz. This enables many operating systems and programs to enjoy a faster and more efficient execution.

The enhanced features of the 80386 have been used by software developers to allow true multitasking to be done. OS/2 has been upgraded to take full advantage of the facilities and functions now available, as have Novell and Santa Cruz Operation (SCO) unix.

With software and operating systems now utilising the 32 bit structure and architecture of the 80386, a replacement for the 80286 microprocessor was developed. This new microprocessor was not better than the 80386 but rather was a downgraded version of the 80386 and is known as the 80386sx processor. The only major changes made to the 80386sx was the restriction of the maximum direct memory access to 16Mb and the restriction of the speed range to between 16MHz and 25MHz. The pricing of the 80386sx is similar to that of the 80286 and, with the virtual mode still available, is a more than adequate replacement for the 80286. American Micro Devices (AMD) have produced versions of the SX which can run with clock speeds of up to 33MHz.

The downward compatibility of the 80386 and the 80386sx microprocessors allows the use of operating systems and software that were originally written for the 8086/8 and the 80286. The operation of the 80386 based microcomputer is restricted to the use the software makes of the 80386 capabilities.

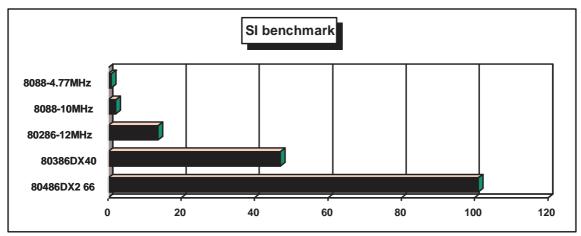

### How the processors improved

#### 80486

Because of a greater demand from microcomputer users for faster and more efficient processing, the 80486 microprocessor was developed. As with the 80386 the 80486 had all of the features of its predecessors, with a few added extras

The Math's Coprocessor was integrated into the chip.

8 kilobyte onboard cache memory was also integrated into the design.

The math's coprocessor is a separate CPU and enables the 80486 to handle floating point calculations. This situation gives a greater flexibility to high end computer users, as the speed of the microprocessor is enhanced considerably.

The Cache memory further speeds up the microprocessor operation, by keeping heavily utilised data in the microprocessor. This also increases the effective speed of the microprocessor. The clock speed range of the 80486 is from 20MHz to 50 MHz. Internal doubling of the clock signal as used in the DX2 type 80486, can take the effective clock speed to 100MHz. The DX4 types which use clock tripling have taken the standard to 100MHz internal, 33MHz external. AMD produced an 80486DX4 120MHz processor which whilst externally clocked at 40MHz, runs at 120MHz internally. This is a replacement for the widely used 80386DX40 cpu.

The 80486 is a 32 bit microprocessor, to keep the standard consistent, as such uses a similar architecture to the 80386. This allows most microcomputers to upgrade from an 80386 microprocessor to an 80486 with the minimum of cost.

A scaled down version of the 80486 was available, designated the 80486SX. The 80486SX restrictions include; a restriction of speed to 33MHz and the loss of the internal math's coprocessor. Clock doubled versions of the SX were available, though these ceased production mid 1995.

### The extensions to the 8086 registers in the 80386/80486

# The 80486DX Block diagram

#### The "Pentium"

The recent processor from INTEL is the "Pentium", which would have been called the 80586 if they had kept to their original numbering scheme. The reason for the change is their inability to stop their competitors from using the number, as it cannot be trademarked as their own. So we have the "Pentium".

The processor is quite different from all the rest in design and has a great many features to enhance performance.

- □ Approximately 3 million transistors

- ☐ 64 bit data bus with additional burst mode operation.

- ☐ A branch target buffer predicts which way execution will branch and executes the opcodes without delay.

- Two instructions can be operated on at the same time in parallel pipelines.

- Built-In multiplier, divider and adder units so floating point instructions can be executed in one clock cycle.

- ☐ Performance is 100 Million instructions per Second at 60MHz operation.

The Pentium surpasses the 486 in speed and power by using 256-bit data paths, pipelined processing that lets operations in all components of the microprocessor happen at once, and instruction processing split into dual arithmetic logic units.

The processor is a 73 pin package arranged in a 21 x 21 pin grid array with an additional pin for keying. The chip incorporates 3.1 million transistors through the use of 0.8 micron CMOS technology. The processor uses a 32 bit bus, but its external data bus to memory is 64 bits wide. A burst mode permits 256 bit data segments to be read by the data cache in a single bus cycle, which produces a maximum memory transfer rate of 528 million bits per Second.

**NOTE:** To obtain maximum performance programs are required to be re-compiled or reassembled using a "Pentium" compiler/assembler. Otherwise the performance upgrade from 486 is less than inspiring.

#### The P6 now "Pentium Pro"

The Pentium Pro has been constructed with the level 2 cache in the chip carrier with the processor. It has complete code compatibility with previous Intel 80x86 processors. It delivers superior performance through an innovation called Dynamic Execution. It also provides support for enhanced data integrity and reliability features: ECC (Error Checking and Correction), Fault Analysis & Recovery, and Functional Redundancy Checking.

The Pentium Pro integrates about 5.5 million transistors on the chip, compared to approximately 3.1 million transistors on the Pentium processor. It operates at clock speeds of 166MHz up to 200MHz.

It initially was produced on the same high volume 0.6 micron process currently used for the 90 & 100 MHz versions of the Pentium processor, and was then moved to a 0.35 micron process.

It is intended for use as in a multiprocessor machine that will deliver performance that will scale up to 1000 MIPS with four processors. It is of course fully backward code compatible, however it has been noted as not running 16bit applications very well. Its 32bit performance is exemplary and is suited to NT, Windows 95 as well as Unix platforms.

#### Klamath and MMX processors

The latest in a long line of processors, the multimedia/graphically orientated processors, Pentium MMX, which speed up graphical operations was released in Jan 1997. Three versions were produced, 166MHz, 200MHz and 233MHz. The P166MMX outperforms the standard Pentium by about 10%. With the Pentium being obsoleted in June/July 97 this processor replaced the standard Pentium as the 'entry level' processor. It didn't last long, on the 21st of October 1997 it ceased production leaving the pc buying public to make a jump in cost to the Pentium II. Stocks of Pentium MMX cpu's are expected to run out around June 1998.

AMD and Cyrix have competing products, though neither has really made it in South Africa. In Europe AMD have made serious inroads into Intel's market with the K6.

#### The Pentium II

This is really a Pentium Pro with corrections applied to the 16bit performance and the MMX instructions added to the design. The socket design is quite different from the previous chips and uses a patented and proprietary socket. This stops any competing processor being plug-compatible. The processing performance is considerably improved over the previous standard Pentiums but leaves the basic PC design 'I/O bound' as the peripherals do not match the processing speed.

The Pentium II has clock speeds of 233MHz to 450MHz, though Intel has shown a version running at 700MHz. The original version came with a large heatsink and dual fans which made the cpu unit heavy and unstable when mounted normally in a motherboard. Newer versions are being produced with single fans and circuitry to check for fan failure.

The Pentium II has also changed the design of the motherboard from the XT/Baby AT design. The new ATX design seen above has the serial and parallel ports as well as USB and PS/2 connections cluster mounted on the motherboard. The motherboard also has power down and power off functions built-in. This all means that the case and power supply is a new design as well allowing for these functions.

With the machine being 'I/O bound', Intel have brought out a high speed graphics attachment bus called AGP. More details further on in the display peripherals section.

\*\*\* More ....

#### **Multiprocessor computers**

Multiprocessor machines can be purchased, consisting of Pentium type processors. This type of pc may well be the future standard for "power" boxes. It is already becoming the 'norm' for file server and database server type machines.

#### 8087, 80287 and 80387 Floating point coprocessors

The math's coprocessor was designed to provide a library of fast floating point routines. The processor requires no additional hardware I/O or DMA transfers. It is accessed using escape sequence codes in software. Most modern compilers have this support built in and some automatically detect the presence of the coprocessor.

The coprocessor has its own set of registers and instructions for access appear in the 8088/6 processor instruction set. There are eight data registers of eighty bits each, a status and control register and an instruction and operand pointer. The registers are also organised as a stack and register addresses are relative to the top of the stack.

Programming the coprocessor is straightforward as the processor has only sixty-nine instructions. The additional processing speed attributed to the use of a coprocessor can be quite amazing. A typical calculation can be reduced in time by thirty times or more by the addition of a coprocessor.

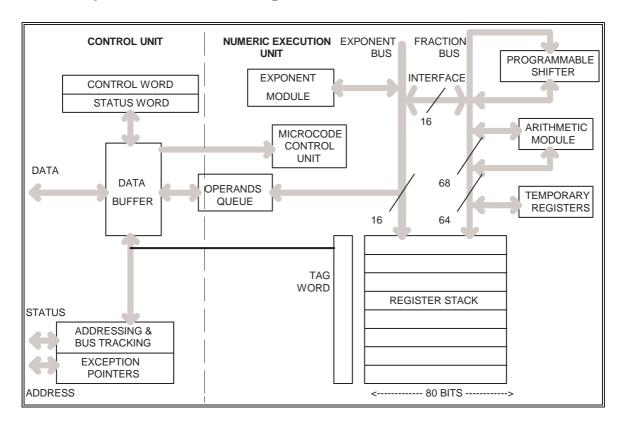

#### 8087 Coprocessor block diagram

# **Support Microcontrollers**

The purpose of the support microcontrollers is to assist the microprocessor in the control of the microcomputer system. The 8088 and 8086 rely on separate microcontrollers mounted on the motherboard. The more complex 80286, 80386 and 80486 have many of the support functions built into the microprocessor chips.

#### **DMA (Direct Memory Access) Microcontroller**

DMA is a concept whereby the CPU is not involved in the transfer of data from a peripheral device to memory, vice versa or memory to memory. The microcontroller usually used, in 8086/8 based systems, is an 8237. The 8237 has four DMA channels that can be individually programmed. Two of these chips were designed into the AT design to provide seven DMA channels 0 to 7. Channel 0 has the highest priority and 7 the lowest. Channels 0 to 3 perform 8 bit transfers and channels 5 to 7 can perform 16 bit transfers in the AT design. Channel 4 is used by the motherboard to cascade channels 0 to 3 to the processor. Channels 0, 3, 5, 6 and 7 are reserved, 1 is for SDLC and 2 is for disk use.

### **Clock Generator and Timing Crystals**

All microcomputer systems require an accurate timing signal, to synchronise the various devices. A timing signal is generated by a quartz crystal oscillator. This signal is made into TTL compatible square waves by a Clock Generator chip. Timing signals of lower frequencies are generated by divider circuits internal to the clock generator chip.

In the case of the 8088 based microcomputer systems, the crystal produces a frequency of 14.31818 MHz. This in turn drives an oscillator circuit that supplies the 8284 Clock Generator. The original frequency is divided by 3, to provide a timing signal of 4.77 MHz, for use by the 8088. The 4.77 MHz signal is divided again by 4 to produce a 1.19 MHz timing signal for use by the timer counters.

The 8284 also handles a logic signal for use by the microprocessor, the Power Good signal. On IBM power supplies this signal is generated when all power levels are stable. The power good signal is used to reset the microprocessor, and start its normal operation.

# **PIT (Programmable Interval Timer)**

This timer/counter microchip is an 8253, and has three 16 bit timer counters attached to the microcomputers bus. The PIT generates an interrupt signal that is used to keep the time of day clock and to operate the speaker. The 8253 also handles the triggering of the DMA microcontroller to start the memory refresh cycle.

### **Programmable Peripheral Interface (PPI)**

An 8255 microcontroller was used for the PPI in the XT. The 8255 is a very versatile device in that it provides 24 programmable input/output lines. The PPI is used for several purposes, these are:

Reading the value of the motherboard configuration switches. Interfacing with the keyboard.

Providing the speaker output control.

Controlling the NMI enable circuitry.

Supplying control lines for the 8253.

The 8255 functions have not been incorporated into any microprocessor design and was not used in the AT and later motherboard designs.

#### The Keyboard interface controller

On the AT/ISA motherboards this is generally a dedicated microcontroller based on an Intel 8042. The chip is programmed to respond to serial data from the keyboard and pass the data to the main cpu via the keyboard interrupt. This controller chip is also responsible for controlling the A20 address line, which allows access to extended memory.

### **Interrupt Controller**

This microcontroller is an 8259. Most microcomputers are driven by interrupts. In the case of the 8088, only two interrupt connections/pins are available, the Non Maskable Interrupt and the Maskable Interrupt. The interrupt controller intercepts interrupt signals from all the devices, attached to the microcomputer system bus, allocates a priority to the interrupt signal and passes on the interrupt to the microprocessor. The 8259 enables 8 extra interrupt levels to be used on 8088 based microcomputer systems. Two cascaded 8259's are used in 80286 machines to provide 15 extra interrupt levels.

# The Floppy disk drive controller

This microcontroller chip was originally an Intel 8272 floppy controller and was later upgraded to a Zilog 765 or NEC chip. The controller is designed to support high density disk drives up to 1.44MB and low density drives down to 160k single sided floppy disks.

#### The hard disk controller

The AT/ISA design used a hard disk controller adapter card based on a Western Digital design. The later cards used a WD1006 chip set which allowed for an interleave of 1:1 on the hard disk and had track buffering. This "Standard" design has been used as the basis for most IDE controller interfaces and is the required standard for use with Windows 32 bit disk access. Performance originally was around 240k Bytes per Second rising to 500k Bytes per Second with the WD1006.

Even though most of the functions, handled by the various support microcontrollers, have been incorporated into the 80286 and above, many microcomputer systems still use these microcontrollers for hardware compatibility.

#### Wait state

The main consideration in the manufacture of a microcomputer system, is the matching of speed. Many systems do not match components correctly, therefore compromising the efficiency of the microcomputer system. The term Wait State describes the number of cycles the microprocessor is inactive waiting for a reply from another device. The device can be memory or an input/output device. Thus the overall performance of a microcomputer system relies on the speed of the slowest device. The AT had one wait state inserted on memory access, which allowed the use of 150 nano Second ram chips.

# Memory, memory addressing & structure

#### Memory

Memory forms an important part of any computer system, as it is used to temporarily store data and programs that are being utilised by the microprocessor. Two types of memory are used these are ROM and RAM.

### **ROM (Read Only Memory)**

ROM contains programs and data that is required by the microcomputer at start up. The contents of ROM cannot be changed, under normal conditions. The programming of ROM is done at the manufacturing stage. ROM is split into further types, these are:

PROM Programmable Read Only Memory

EPROM Erasable Programmable Read Only Memory

EEPROM Electrically Erasable Programmable Read Only Memory

A PROM is basically ROM that has not been programmed. The programming is done by the user, by using a special PROM programming unit. Once programmed the PROM cannot be reprogrammed.

The EPROM may be reprogrammed, in the same way as the PROM, but only after the contents have been erased. This is done by subjecting the microchip to ultra violet light for 40 to 45 minutes.

**Eproms**

EEPROM allows the reprogramming to be done without having to erase the previous memory contents.

ROM chips on the motherboard, may contain the BIOS (Basic input/output System), the initialisation routines for the microcomputer system, diagnostic routines, the routine for handling the diskette boot procedures, system configuration and BASIC (Beginners All-purpose Symbolic Instruction Code) interpreter. In most cases the POST (Power On Self Test) is also included.

Other uses for ROM on the motherboard are to store programs that run directly on power-up, such as dedicated word processing and proprietary control software.

ROM has a disadvantage in that the memory access is generally slow, in comparison to RAM. This has lead to some manufacturers programming the BIOS to copy the ROM into RAM on startup, providing an improvement in performance. This "SHADOW" RAM is however lost to the operating system as a result.

Flash eprom technology has already been used for network adapters. It may soon be the norm for motherboards allowing BIOS upgrade from a disk. Some Pentium motherboards already have this as an additional feature.

### RAM (Random Access Memory)

RAM is split into 2 further types; these are SRAM (Static Random Access Memory) and DRAM (Dynamic Random Access Memory). RAM generally has faster access than ROM, however RAM has the disadvantage of being volatile. That is: when power is removed from static or dynamic RAM, the contents disappear.

Dynamic RAM uses small capacitors mounted on a grid of lines. The capacitors hold a charge that signifies a binary 1. When RAM is read, the capacitors are automatically recharged. DRAM capacitors discharge fairly quickly (4mSec), so a refresh cycle is required to automatically recharge the small capacitors. The refresh is really a memory read on a block of cells, and this is done transparently by the memory refresh hardware many times per second.

Static ram uses transistor flip-flops that can store data for long periods of time, as long as power is supplied to the RAM chip. The access time for SRAM can be extremely fast. The CMOS (Complementary Metal Oxide Semiconductor) RAM that is used to store system information on 80286 systems is static ram. The content of the CMOS RAM is variable according to system set-up. The SRAM is used because the memory chip only requires a low level of power, and this can be supplied by a battery pack.

**NOTE:** Both ROM and RAM memory chips are sensitive to static electricity and to protect these components they should be carried in anti static tubes or containers.

### Parity - Hardware error detection

In any sequence of bits parity can be calculated on those bits according to even or odd parity. In the PC this is done by a hardware chip and stored into the ninth memory location. Should the bit generated by the parity check chip not correspond to the bit stored in the ninth bit, a parity alarm signal is generated. The parity alarm signal is connected to the Non Maskable Interrupt line and produces the message "system parity error: system halted".

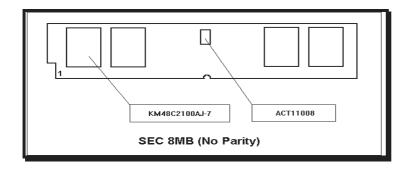

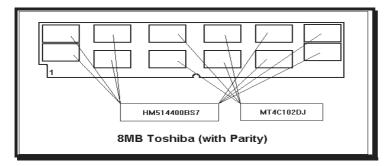

Unfortunately some SIMM manufacturers make SIMMs with and without parity. This leads to problems, as you cannot mix the two types on the motherboard. You may disable parity checking if you have a late model motherboard, allowing both to be used. How do you tell which SIMM has parity or hasn't? Count the number of chips on the SIMM. If a SIMM has 9 chips or a multiple of 9 then it will have parity.

#### Mix-n-Match its not

Mixing SIMMS of different manufacturers is also a recipe for disaster, as access time differences will produce parity errors or worse, unexplained crashes. Similarly different construction SIMMs will produce errors. The OLD SIMMs would have nine 1M Bit chips on a SIMM, whereas the new variety have two 4 bit chips and a 1 bit parity chip. These cannot be mixed reliably in a machine.

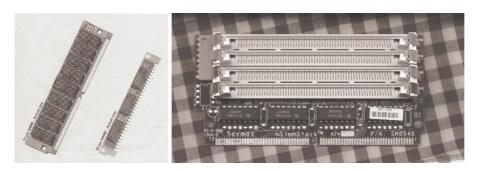

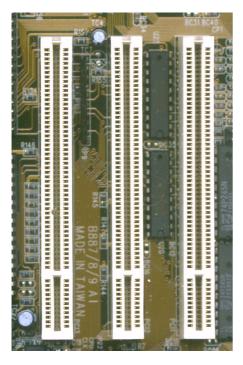

72 pin and 30 pin SIMMs

A 'SIMM-VERTER' allows you to use up those 30 pin SIMMs

# **Memory Addressing**

Each memory or port component in the PC has a unique address. A given I/O adapter may have both an I/O address and memory addresses. The memory addresses are for the memory on that card. For example, a VGA card has a given I/O address for the 6845 video controller, and the RAM on the card, used for the text and graphics, has a memory address.

The lowest memory addresses, below 640k are for motherboard RAM and are used to store the interrupt vector table, the BIOS data area, the DOS working area and the user's programs.

An 8086 processor has 20 address lines resulting in the addressing of 1,048,576 bytes of memory. The 8086 having only 16 bit registers has to add two registers together to obtain the required 20 bits. This is done with a segment register and an offset register. The address in the

offset register is offset 4 bits from the physical address and the two values are then added to obtain the physical address. This 20 bit address is then placed onto the address bus.

The 80386 and 80486 has 32 address lines and can address 4,294,967,296 bytes of memory in its virtual protected or native mode.

NOTE: Its called 'real mode' because the address specified in the segment and offset, actually refer to a physical address in memory.

**CPU addressing** - how it works. Byte addressing and Word addressing.

The 8088 had 16 bit registers and an external 8 bit data bus. The 8086, 80186 and 80286 all had 16 bit registers as well as 16 bit external data buses. This meant that these processors had an advantage of being able to transfer 16 bits at a time over the data bus, rather than two 8 bit bytes. This speeds up the retrieval of data from memory. With the 80386 and up this becomes 4 bytes per memory access. This all supposes that the data is aligned on either a word boundary or double word boundary. If it isn't the cpu will have to have two or four retrievals to obtain the data. Compilers and assemblers can be instructed to place the data on word or double word boundaries, thus making programs perform better when a higher processor is used.

#### **Intel Notation**

The original 8080 (not 8088) processor stored its 16 bit words with the high byte in the higher memory location. This method has carried on throughout the Intel range of processors. Other manufacturers of processors, such as Motorola use the lower memory location for the highest byte. This leads to interesting data conversion problems between systems of different processors. If a 16 bit number is read from memory you will have to transpose the right byte value and the left byte to obtain the correct value. A 32 bit number is stored in a similar manner, with the highest byte of the four bytes, stored highest in memory.

Example: The pointers stored in the interrupt table are stored like this:-

[OFFSET] : [SEGMENT]

[low byte][high byte] : [low byte][high byte]

# **Looking at Memory addresses with Debug**

Debug has been provided with DOS since version 1.0. It provides a system monitor program which can be used for 'debugging' programs. For a detailed manual see the document DEBUG.txt.

Debug commands and functions include:

Compare 2 blocks of a system memory

Display contents of system memory

Display and modify the content of system memory

Fill the memory with data or data from a string

Go and execute the program from an address.

Specify break points in a program and display system status

Load data from a diskette into memory

Move the contents of memory from one location to another.

Send data to an I/O port.

Display the contents for the processor registers and flags.

The "Barefoot" Engineer Course (BFENG.doc)

Search system memory for data specified in a string.

Trace the execution of a program and display processor CPU status.

Disassemble an assembly language program.

Write a block of system memory to diskette.

Debug is a command driven program and as can quickly be seen, it was designed for programmers. The hyphen "-" is used as the prompt. To obtain some help, type a ? and press enter.

To examine a block of memory start DEBUG from the DOS prompt and after the "-" appears, type in D40:0 and press Enter. This will give a "D"ump of the memory at segment 40 hexadecimal in both hexadecimal and ASCII.

A memory address is a physical location within the total memory, at which data can be stored. Under DOS, memory is divided into segments each of which comprises 64 k of contiguous bytes of memory. An individual memory address within a segment is called an offset. The first byte in a segment is offset 0 the second is offset 1 etc. Individual memory addresses are identified by their segment address and offset. Debug knows nothing about extended memory and cannot be used to examine memory above 1MB.

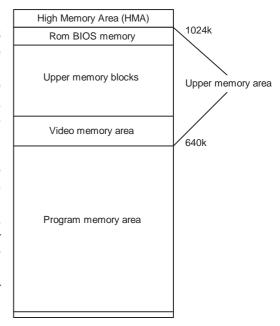

# The PC's Memory Structure

# The XT & AT System memory map

| Decimal            | Hexadecimal                        | Function                                                    |

|--------------------|------------------------------------|-------------------------------------------------------------|

| (k = 1024)<br>960k | (absolute physical) FFFFF to F0000 | 64k system ROM BIOS, Power On Self-Test and possibly BASIC. |

| 816k               | EFFFF<br>to<br>CC000               | Reserved for ROM attachments on adapters.                   |

| 800k               | C0000                              | VGA ROM bios attachment                                     |

| 736k               | B8000                              | CGA adapter display memory.                                 |

|                    |                                    | Monochrome & Hercules adapter display memory.               |

| 704k               | B0000                              |                                                             |

| 640k               | A0000                              | EGA / VGA adapter graphics display memory.                  |

|                    | 9FFF<br>004FF                      | DOS & USER memory<br>(Read / Write memory.)                 |

| 1024<br>0000       | 00400<br>00000                     | BIOS DATA AREA<br>Interrupt vector table                    |

# Port & I/O Addressing

Port addressing is done by the processor in exactly the same manner as memory addressing. The difference being that the processor asserts the IOREQ control line. The 8088 can address 65536 individual ports using the lowest 16 bits of the address bus to select the required port. The IBM XT designers however provided only for 1024 ports and grouped them in blocks of eight. This was changed in the AT design to the full 64k ports and grouped in blocks of 32. Some adapters designed for the XT do not decode the port address fully and can be found at several addresses on the 64k map.

### XT (8088) I/O Address map

| Address range (Hexadecimal) | Usage                                              |

|-----------------------------|----------------------------------------------------|

| 3F8-3FF                     | Asynchronous Communications (Com1)                 |

| 3F0-3F7                     | Diskette controller                                |

|                             |                                                    |

| 3E0-3E7                     | Reserved                                           |

| 3D0-3DF                     | Colour Graphic display adapter. (CGA)              |

| 3C0-3CF                     | Reserved                                           |

| 3B0-3AF                     | IBM Monochrome Display adapter.                    |

| 3A0-3AF                     | Reserved                                           |

|                             |                                                    |

| 380-38F                     | SDLC Communications adapter                        |

| 378-37F                     | Parallel Printer                                   |

|                             |                                                    |

| 320-32F                     | Fixed Disk controller                              |

| 300-31F                     | Prototype Card (USER I/O)                          |

| 2F8-2FF                     | Asynchronous, Communications (Com2)                |

| 2F0-2F7                     | Reserved                                           |

| 278-27F                     | Reserved                                           |

| 220-24F                     | Reserved                                           |

| 210-217                     | Expansion Unit                                     |

| 200-20F                     | Game Control & Tape streamer hardware.             |

|                             |                                                    |

| 0Ex                         | Reserved                                           |

| 0Cx                         | Reserved                                           |

| 0Ax                         | NMI Mask Register (x indicates don't care) (bit 7) |

| 080-083                     | DMA Page Registers                                 |

| 060-063                     | PPI 8255                                           |

| 040-043                     | Timer 8253                                         |

| 020-021                     | Interrupt 8259                                     |

| 000-00F                     | DMA Chip 8237                                      |

NOTE: When powering-up the NMI (Non Maskable Interrupt) for the 8088 is switched off.

The switch (mask) can be set and reset as follows:-

Set mask: write hex 80 to I/O Address hex A0 (enable NMI) Clear mask: write hex 00 to I/O Address hex A0 (disable NMI)

# AT & ISA I/O Address Map

| Address range<br>(Hexadecimal) | Usage                                               |

|--------------------------------|-----------------------------------------------------|

|                                | space for other adapters ?                          |

|                                |                                                     |

|                                |                                                     |

|                                |                                                     |

|                                |                                                     |

|                                |                                                     |

|                                |                                                     |

|                                |                                                     |

|                                |                                                     |

|                                |                                                     |

|                                |                                                     |

|                                |                                                     |

|                                |                                                     |

| 378-37F                        | Parallel Printer port 1                             |

| 320-32F                        | not used                                            |

| 300-31F                        | Prototype Card (USER I/O) or Ethernet adapter card. |

| 2F8-2FF                        | Asynchronous, Communications (Com2)                 |

| 2F0-2F7                        | Reserved                                            |

| 278-27F                        | Parallel printer port 2                             |

| 220-24F                        | Reserved                                            |

| 210-217                        | Reserved                                            |

| 20C-20D                        | Reserved                                            |

| 200-207                        | Game Control & Tape streamer hardware.              |

| 1F0-1F8                        | Hard disk controller.                               |

| 0F0-0FF                        | Math coprocessor I/O                                |

| 0C0-0DF                        | DMA Controller no 2 8237                            |

| 0A0-0BF                        | Interrupt controller 8259 Slave                     |

| 080-09F                        | DMA Page Registers                                  |

| 060-06F                        | 8042 Keyboard controller                            |

| 040-05F                        | Timer 8254                                          |

| 020-03F                        | Interrupt controller 8259 Master                    |

| 000-00F                        | DMA Controller 8237                                 |

# **Peripheral Devices**

### Display adapters

[Speed of graphics, why 16 bit has fewer wait states, why mono/cga is poor for graphics speed. Why local bus is really good for graphics.]

### **Color Graphics Adapter \***

[\* Yes I know it is spelt wrong!]

Monochrome and CGA adapter cards worked by making the processor have complete access to the display memory. These cards relied upon the processor being patient as the CGA card would give "SNOW" if it was accessed during a normal scan display time. The processor therefore had to wait for a flyback time to access the memory, several microseconds later. The BIOS was written to allow for this or alternatively the CGA adapter would be "switched off" during update. This gave rise to a blinking or flashing display which was awful to watch.

Later adapters, both Hercules and CGA clones, used the WAIT signal on the processor to stop the CPU from accessing the memory until it was available without causing "SNOW". The EGA (Extended Graphics Adapter) had this wait state circuit built in and was snow free as a result.

# The VGA adapter

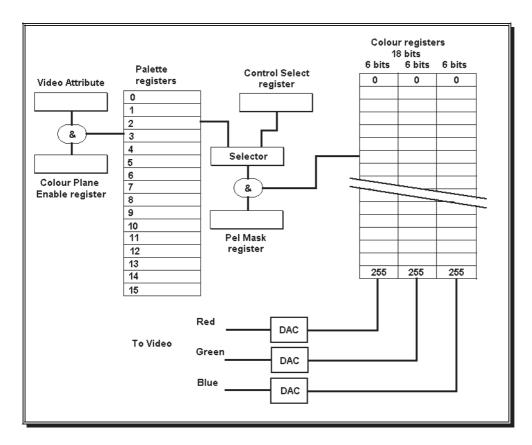

An improvement brought about by IBM for the PS/2 range of computer, the VGA adapter has stuck with the industry. The successor the XGA has not caught on. This adapter is an ANALOGUE type of video display where previous display adapters were DIGITAL. There is a sort of perverse logic to this as the Digital to Analogue converters have improved to 24 bit from the initial 6/8 bit converters allowing millions of shades of the primary colours. This renders picture quality approaching photographic quality. It is certainly far better than television quality.

**Original VGA adapter** - allows 18 bit colour registers, 6 bits per primary colour giving 262,144 total colours.

VGA eliminated most of the wait states used in previous cards and allowed the processor the full 16 bit bus access to the screen display memory. This improved the performance dramatically from typically a few hundred characters per millisecond to 700 characters per millisecond for a 256k VGA card. The performance improves with amount of memory as well as cpu speed and a 512k adapter can give up to 2,900 characters per millisecond on an ISA bus.

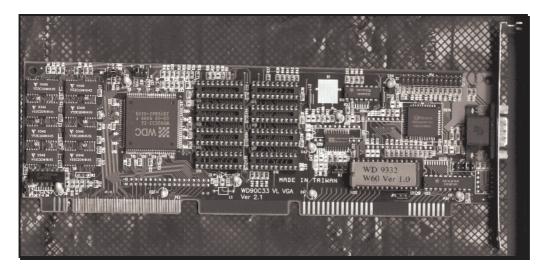

#### Local Bus VGA adapters

Tests carried out by us indicated that a four to five times improvement could be achieved with a local bus VGA card over a standard 512k VGA ISA card. The fastest we tried, the WD90C33 VL BUS VGA card gave nearly 10,000 characters per milliSecond compared to 2,500 characters per milliSecond for a Tseng Labs or Trident VGA adapter card. The price difference is minimal if you compare costs for a 1MB Trident VGA adapter against this card which comes supplied with 1MB.

Some adapter cards provide extra processing capability in the drawing of graphics shapes and as a result provide extra speed in operation. These are generally referred to as "Accelerator" video adapters.

An example of an accelerator card was recently tested by us, the Chips & Technologies "Wingine" provides a number of performance enhancing routines in its bios and caches fonts as well. It is a local bus adapter and costs no more than a standard VGA 1MB adapter. Its performance measures around 16000 characters/mSecond.

#### **PCI VGA cards**

Most PCI VGA adapters have moderate performance, lower than the VL-BUS types. However these are now the standard. For top notch performance use a Diamond Stealth 64 card.

PCI VGA adapter

Note the card is the other way around from an ISA card. This is because the PCI slots face the opposite way to stop incorrect insertion of ISA cards. It also loses one available slot (ISA or PCI) as the slots that are together cannot both have cards in them.

Trident AGP card. Note the staggered connections on the connector.

# **Accelerated Graphics Port - AGP**

With the Pentium II comes a dual bus operation that puts the cache memory connected to the cpu via a 1G bits per second bus and a front side bus that runs at 528M bps. The PCI bus is connected via a chip set to the front side bus. This bus in most machines has to contend with a vast amount of data traffic going to the display adapter especially when displaying video.

By making the front side bus switched Intel have provided a 528Mbps connection to the main memory, a 528Mbps connection to the AGP port and a 132Mbps connection to the existing PCI bus. Keeping the high volume data traffic off the PCI bus will improve the peripherals speed of operation.

# Parallel and Serial communications

#### Voltage levels

Signalling between equipment is generally done at low voltages and currents to ensure safety of test personnel. In the next section I discuss the RS232C connection between equipment and in the section after, the printer port connection.

Parallel transfer of data is generally done at least 8 bits at a time and sometimes 16 bits at a time. A single line extra is used to signal the receiving device that the data is valid. This technique is used to transfer data to and from the cpu as well as to peripheral devices. It is generally faster than serial communication of data. It is used by the highly successful LapLink and other file transfer programs to transfer data from one pc to another.

Serial data transfer is carried out one bit at a time, which means slower data throughput than parallel transfer. It also means more complicated hardware requirements, usually a UART or USART.

#### Serial data communications and UARTS

Serial data is transferred one bit at a time. Morse code is a form of serial data. Morse was superseded by 5 bit teleprinter codes commonly called Baudot. In America they will say Murray code. Five-bit code was and still is being used day in day out to transfer textual information from one side of the world to the other. Send a telegram to someone and the post office will use a teleprinter to transfer the message using five-bit Baudot code.

In more recent times it was more desirable to send more detailed text, using lower case as well as capitals. ASCII the standard character definition has become the order of the day. ASCII is truly a seven bit code, allowing for 128 possible characters. Extensions to ASCII were introduced by IBM in the PC to allow some line characters as well as some accented characters.

ANSI the American National Standards Institute are busy with a global version of ASCII, which may replace ASCII in computers of the future.

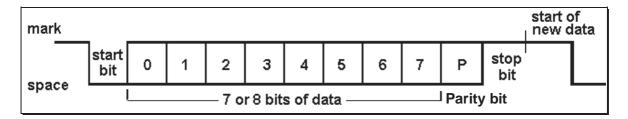

#### Serial data stream

The diagram represents a series of data bits against a period of time. The data rate is described as either "bits per second" or the "Baud" rate. Baud from Msr Baudot, the inventor of the five bit code. Obviously the rate description is dependent upon how many bits are used to contain a character. This could be 8 data bits with even parity and two stop bits, giving a total of twelve bits. So when quoting a data rate ensure that the number of data bits etc are stated.

The start bit is used in asynchronous data to signify the start of a character and allows the receiver to synchronise its local clock. The receiver will then wait a half bit period to see whether it is a true start bit. This provides some immunity to noise as most noise pulses will not last a half bit period. If the bit is still low, the receiver will then wait a full bit period and check for a high or low line voltage. If low it is a "0", if high it is a "1". The corresponding bit value is then placed in a bit of a register. The process is then repeated for all the expected bits of data.

The parity bit (P in the diagram on the previous page) provides some further error checking for the complete data byte and is set according to whether ODD or EVEN parity is being used. The receiving software will usually discard the byte received if the parity bit received is incorrect. The receiving chip will usually set a bit in a status register to tell the cpu that a bad parity data byte was received.

The stop bit is a hangover from the old days when the receiving device was a mechanical teleprinter which took a fair amount of time to "digest" the character received. It is not really needed when UART chip to UART communication is carried out. Unfortunately it is not an optional setting and is still transmitted. A UART is an acronym for Universal Asynchronous Receiver Transmitter, which is the chip used by the computer to send and receive data serially. The "norm" is one stop bit for computer to computer transfers and two stop bits for transmitting to a printer.

Seven or eight data bits may be transmitted and received and quite a few UARTS allow five or six bit operation as well. The UART used by IBM in the IBM PC was the 8250 type. This chip had an unfortunate habit of emitting spurious interrupt signals and the BIOS of the PC and XT was designed to allow for them. When IBM designed the AT 80286 machine, they used a later version of the chip called an 16450. This UART does not emit spurious interrupts and can be run at higher data rates.

**NOTE:** Quite a few XT serial adapter cards have been installed in AT's, much to annoyance of the service or support persons who have had to replace them later. If the UART is an 8250 in an AT, then assume that replacement may well cure problems with lost characters etc.

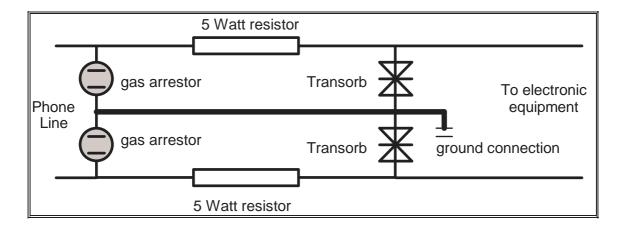

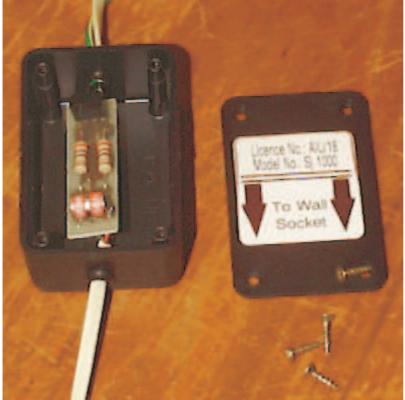

When the PS/2 was released by IBM in 1987, the serial adapter used a 16550 UART. This chip is a vastly improved and featured version of the 8250. Unfortunately IBM did not know about the manufacturing problems and large numbers of PS/2's could not make use of the features in the UART. The 16550A replaces the faulty chip and provides a FIFO buffer arrangement that dramatically improves the performance. Windows 3.1 can make use of the FIFO buffers in its serial drivers.